## LSIの話

# -loT社会を支えるハードウエア-

元 産業技術総合研究所・工学博士 木 英

#### ◆経 歴◆

1972~2001

工業技術院電子技術総合研究所電子デバイス部 (主任研究員・ラボリーダー)

2001~2008

産業技術総合研究所エレクトロニクス研究部門 (副部門長、主幹研究員)

2008~2014

産業技術総合研究所産学官連携推進本部 (産学官連携コーディネータ) 産業技術総合研究所イノベーション推進本部 (イノベーションコーディネータ)

2014~2017

日本科学技術振興機構 (JST) ImPACTプログラム (プログラムマネージャー補佐) 1999~2007 東京理科大学客員教授

2012~2015 埼玉大学非常勤教授

### 1. はじめに

本稿は、筑波経済月報2020年4月号(No.81) に掲載された「LSIの話―IoT社会を支えるハード ウエア― | の後編です。

前編では、LSI(大規模集積回路)を構成する電子 材料としての半導体の特徴をはじめ、シリコン (Si)という理想的な半導体の長所、なぜ、MOS 電界効果トランジスタがLSIに使われるかについ て説明しました。

後編では、MOS電界効果トランジスタがLSIに 使われる理由の続きから筆を進めていきたいと思 います。

### 2. CMOS回路とLSI

LSIの驚異的な発展を可能にしたものは、 n-MOSとp-MOSをつないだCMOS(相補型MOS) 回路です。

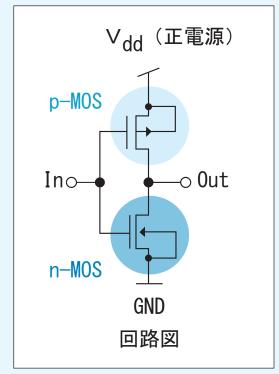

図1は、最も基本的なCMOSインバータ回路 を示しています。p-MOSとn-MOSを直列につな ぎ、共通のゲートを入力端子とし、直列の真ん中 から出力を取ります。

この構成では、一方のトランジスタがONで あれば、他方はOFFになります。入力が正"1"の 場合は、n-MOSがONとなり出力がゼロ"0"になり、 ゲート入力が負またはゼロ"0"の場合はp-MOSが

■図1 CMOSインバータ (NOT回路) の回路図

ONとなり、出力は $V_{dd}$ "1"となるので、入出力が 反転したインバータとして動作します。インバー 夕が実現できれば、論理演算に必要な回路 (NOT, NAND, NOR) は全て構成できます。

CMOS回路では、n-MOS、p-MOSのどちらか がOFFになって定常的には電流は流れず、スイッ チングの時間しか電流は流れないので、低消費 電力を実現できます。

膨大なトランジスタを作り込むLSIでは、低消 費電力が決定的に重要になり、大部分のLSIは CMOS回路で構成されます。

### 3. LSI開発の歴史と展開

LSIの開発の歴史の中で、最も重要な指針は、 インテルの創始者の一人であるGordon Moore が1965年に見いだしたムーアの法則です。

すなわち、半導体集積回路の密度は18ヶ月で 2倍に、3年で4倍になるという経験則です。50 年以上前に示されたこの経験則が、現在に至るま で、基本的には成り立っていることは驚異的なこ とです。

ムーアの法則を実現してきた考え方は、スケー リング則です。表1は、電界を一定とした最も基 本的なスケーリング則を示しています。

Kを1以上とし、素子の全ての寸法を1/Kに比例縮小した場合のデバイスおよび回路パラメータのスケーリング因子を示します。

例えば、Kを2とすると、電圧も電流も1/2、

消費電力は1/4、集積密度は4倍になり、ムーア の法則を満たすと共に、スケーリング則の有効性 が分かります。

ただし現在、最先端では基本寸法が10nmを切る まで縮小されており、さらにスケーリングを行う には大きなブレイクスルーが必要になります。

前編で述べましたように、LSIはあらゆる所で使われており、実に様々なLSIがあります。ロジックLSIでは、カスタムLSIと標準(汎用)LSIに分けられ、用途が明確に決まっているものが前者で、使い方により多様な用途に用いられるものが後者です。

後者に分類されるFPGA (Field Program Gate Array) は、ソフトによって用途や機能を自由に替えられるLSIで、IoTあるいはAI向けのLSIとして注目されています。

なお、本稿では、LSIの基本的な部分に限らせていただいたため、メモリ階層については割愛しました。

#### (I) デバイスパラメータのスケーリング

| スケーリング比 |

|---------|

| 1/K     |

| 1/K     |

| . 1/K   |

| 1/K     |

| 1/K     |

| A K     |

| 1/K     |

|         |

注 K>1

#### (Ⅱ)回路パラメータのスケーリング

| 電流 I                      | 1 ///   |

|---------------------------|---------|

| ⇔■ <i>C</i> Λ //          | 1/K     |

| 容量 $C=\varepsilon A/t$    | 1/K     |

| 回路あたりの遅延時間 $VC/I$         | 1/K     |

| 回路あたりの消費電力 VI             | $1/K^2$ |

| デバイス面積 <i>A</i>           | $1/K^2$ |

| 消費電力密度 VI/A               | 1       |

| 線抵抗 $R_L = \rho \ell / A$ | K       |

| 相対的な電圧降下 IRL/V            | K       |

| 応答時間 RLC                  | 1       |

| 電流密度 I/A                  | K       |

| 電界 E                      | 1       |

■表1 MOSFETのデバイスパラメータと回路パラメータの比例縮小(スケーリング)則(電界一定)